目的

提供逻辑分析仪在 HDQ 总线除错与分析之快速应用方案。

方法

硬件连接

连接逻辑分析仪的通道0至 Texas Instruments 的开发工具 EV2300 上面的 HDQ 脚位,并接好地线。该TI的模块主要是用来检测笔记型计算机电池容量的状态,不过本例,未使用笔记型计算机电池做为待测物,如图1。

图 1

图 1硬件设定

设定取样率

原则上取样率为待测物频率的4-6倍左右最合适;但是取样率越高可以看到越细致的讯号

波形。HDQ 的传输率为16KHz 或142KHz左右。本例使用100KHz的取样率,如图2。

图 2

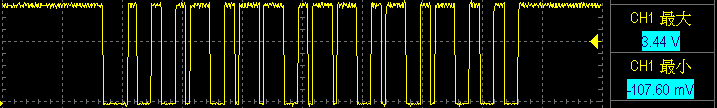

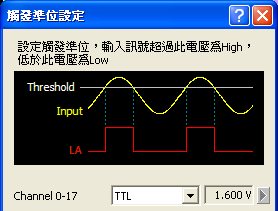

图 2设定触发准位

在设定触发准位之前,建议可使用示波器来观察 HDQ 的讯号波形,来确定触发准位电

压值。

图 3

图 3

图 4

图 4设定触发参数

可以根据需求来设定,本例以CH-00通道( HDQ 讯号)变化缘为触发,如图5。

图 5

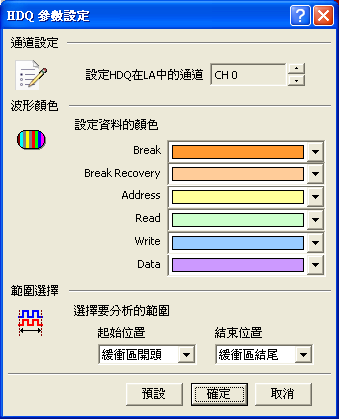

图 5软件设定

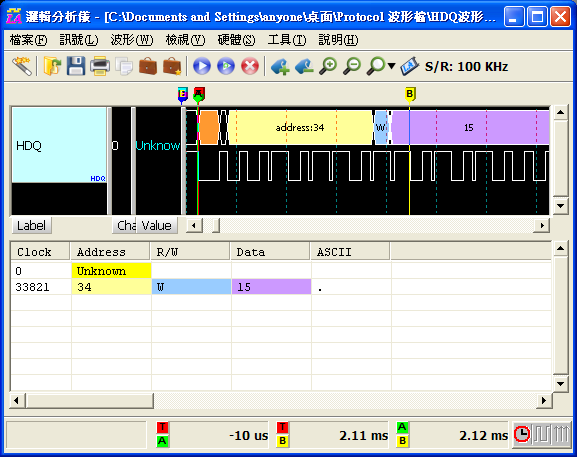

硬件设定完毕之后,进行下列软件设定步骤,如图6,再让逻辑分析仪撷取 HDQ 讯号,并用总线分析软件来做分析,如图7。

通道设定:HDQ 为CH 0。

波形颜色:设定 HDQ 栏位颜色。

选择要分析的范围:预设的整个缓冲区,按下确定,即分析 HDQ 的讯号。

图 6

图 6

图 7

图 7HDQ 通讯协定

HDQ统是用单一讯号线连接主机( Host )和设备( Slave ),但可像 I2C,SPI 一样,同时传输时钟( clock )和资料( data ),而且资料传输是双向的,主机通常为一个电池监控IC。HDQ 使用较低的资料传输速率,最大的传输速率大约 5Kbits/s。讯号线在闲置的状态为高电位,当要传送资料时,固定由主机发出讯号。

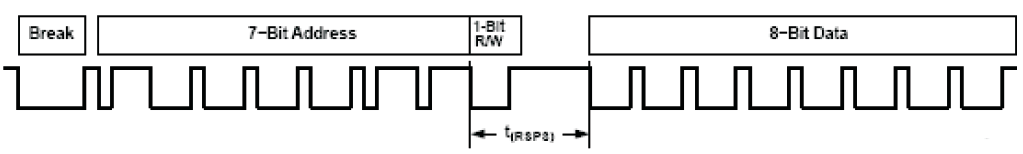

Protocol 的传送是由 Command Block 和 Data Block 所组成。Command 必定由 Host 送出,包含7-bit Address 和 1-bit Read/Write;Data Block 一般只有 8-bit Data,某些IC有支援到16-bit Data。如图8。

图 8

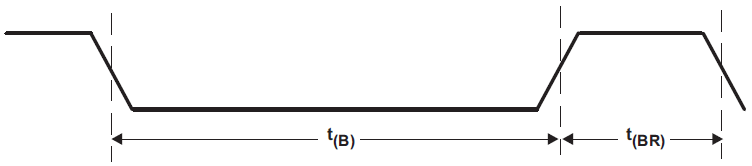

图 8Break

由 Host 发出,将资料线拉到低电位,维持至少t(B)的时间,如图8。

Break Recovery

当 Host 发出 Break 之后,必须等待t(BR)的时间,如图9。后面就紧接着资料的传递。

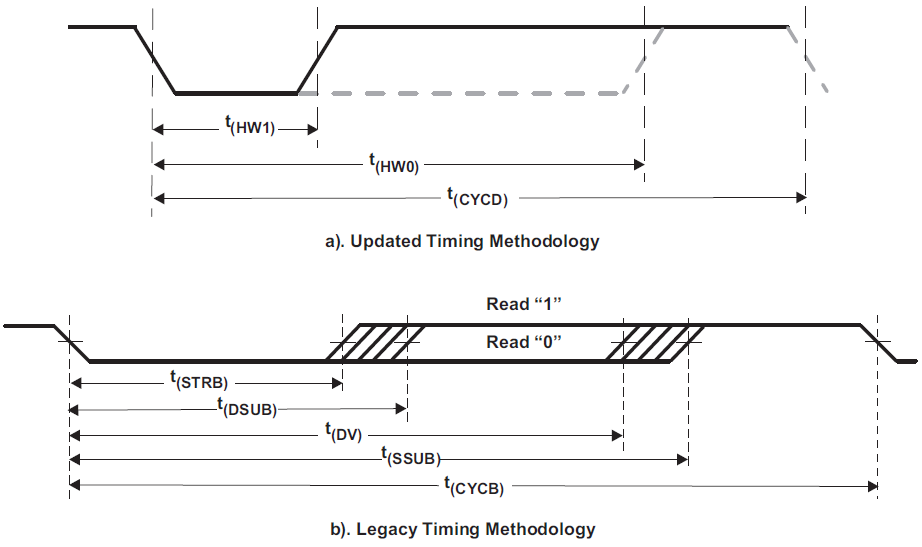

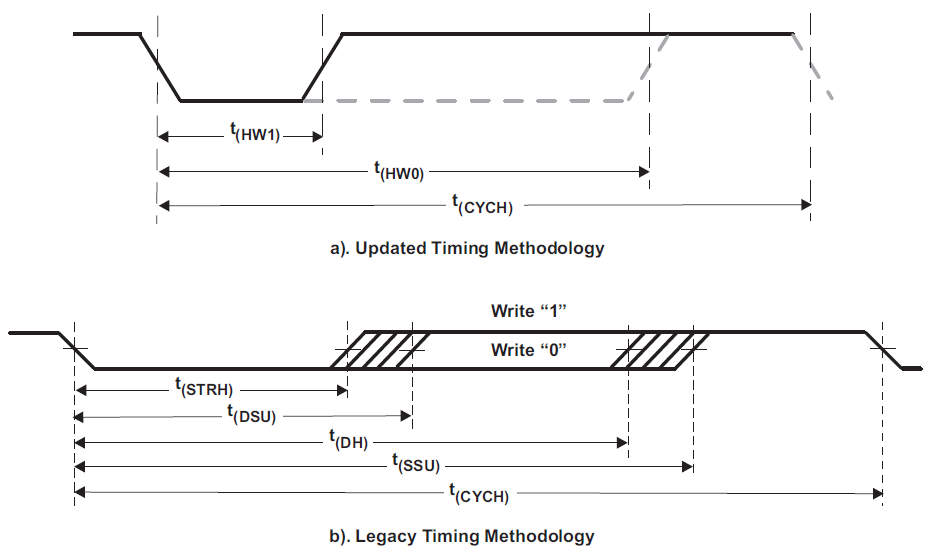

Host Transmitted HDQ Bit

分为 Write-One 和 Write-Zero。

Host 将讯号线拉至低电位,并且在t(HWI)的最大时间之内释放,使讯号在线升为高电位,此为 Write-One,如图10 a)。

Host 将讯号线拉至低电位,并且在t(HWO)的最大时间之内释放,使讯号在线升为高电位,此为 Write-Zero,如图10。

t(HWI)的范围应在t(STRH)和t(DSU)之间;t(HWO)的范围则应在t(DH)和t(SSD)之间。如图10 b)。

图 10

图 10Slave Transmitted HDQ Data Bit

Slave 传送的资料称为Read Data。与Write Data 的差别,只在于资料由不同的地方发送。

t(HWI)的范围应在t(STRB)和t(HWO)之间;t(HWO)的范围应在t(DV)![]() 和t(SSUB)之间。如图11。

和t(SSUB)之间。如图11。