目的

提供逻辑分析仪在UNI/O总线除错与分析之快速应用方案。

方法

硬件连接

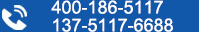

连接逻辑分析仪的通道0至支援UNI/O的Serial EEPROM 的SCIO脚位及两边的接地脚,如图

1, 该实验板为Microchip DV243003,EEPROM为11XX160系列。

图1

图1硬件设定

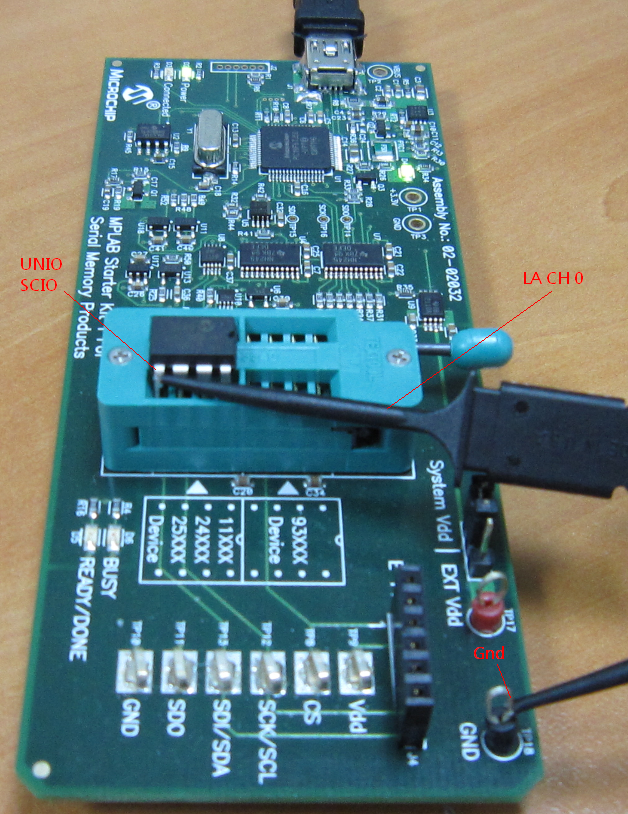

设定采样率

原则上采样率为待测物频率的4~6倍左右最合适;但是采样率越高可以看到越细致的讯号

波形。UNI/O最大的传输率为100KHz左右,而该讯号实际量测的传输率约为80KHz。本

例使用10MHz的采样率,如图2。

图2

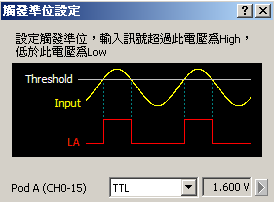

图2设定触发准位

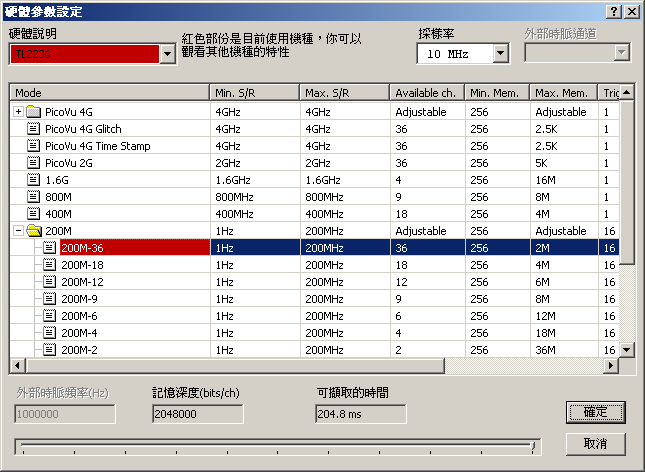

在设定触发准位之前,建议可使用示波器来观察UNI/O的讯号波形,来确定触发准位电

压值。

图3

图3

图4

图4UNIO讯号的电压最大值及最小值分别为5.06V和-125.01mV左右,所以逻辑分析仪的逻辑准位使用预设的1.6V TTL准位即可,如图3和图4。

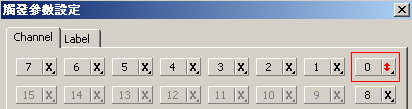

设定触发参数

可以根据需求来设定,本例以CH-00通道(UNI/O SCIO讯号)变化缘为触发,如图5。

图5

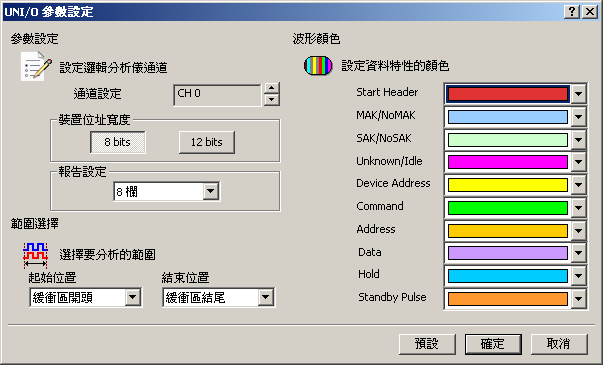

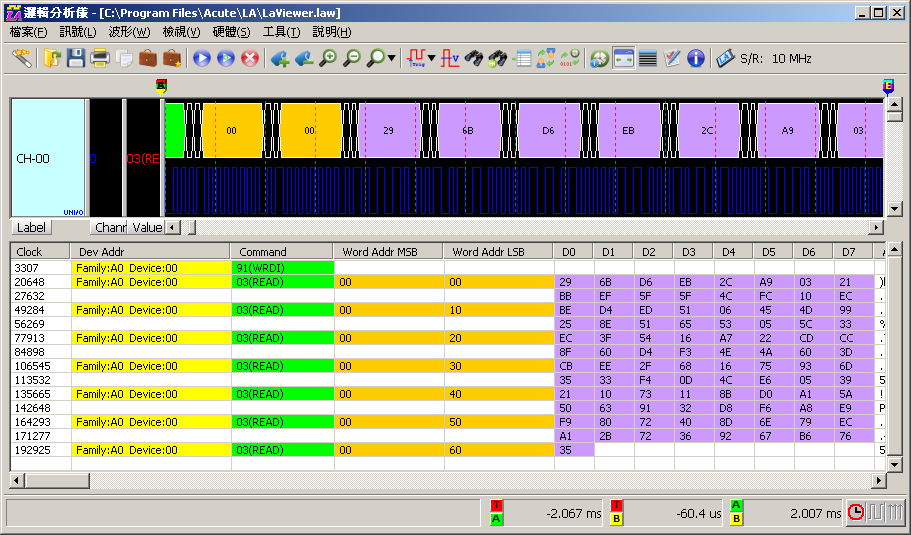

图5软件设定

硬件设定完毕之后,进行下列软件设定步骤,如图6,再让逻辑分析仪采集 UNI/O讯号,

并用总线分析软件来做分析,如图7。

通道设定:SCIO为CH 0。

装置位址宽度:该例装置位址宽度为8bits,所以勾选8bits。

报告设定:显示资料方式为预设的8栏。

选择要分析的范围:预设的整个缓冲区。

波形颜色:最后设定UNI/O栏位颜色,按下确定,即分析UNI/O的讯号。

图6

图6

图7

图7UNI/O通讯协定

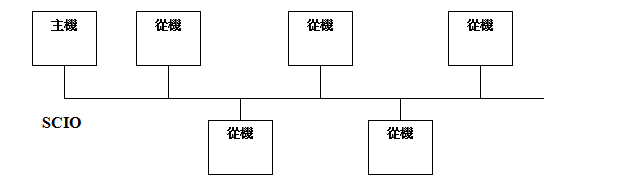

随着嵌入式系统的微小化,针对I/O脚位少量化的需求也越来越殷切,UNI/O通讯协定就是在这样

的时空背景下诞生的。UNI/O是由Microchip制定的,它仅需要一根I/O脚(SCIO)就可以做装置间

的沟通。

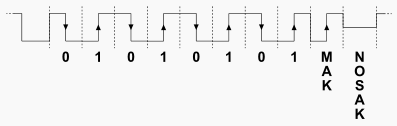

UNI/O支援的资料传输率为10kbps~100kbps,传送的资料会经过曼彻斯特编码(Manchester Encoding)

,为一个主机多个从机的系统架构,参考图8。

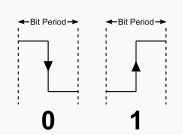

位元编码(Bit Encoding)

图9

图9UNI/O讯号是由时脉和资料讯号结合而成,然后经由曼彻斯特编码之后再将讯号传送。这代表每个资料位元都是以相同的固定时间被传送,该时间称为位元时间(Bit Period)。而根据曼彻斯特编码规则,位元值是由位元时间中的讯号转态时来决定;由高电位转态为低电位为0;低电位转态为高电位为1,如图9。

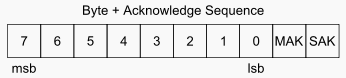

资料宽度(Data Words)

图10

图10UNI/O的资料宽度为8bit,资料的传送方向为MSB->LSB。一个完整的资料传送过程,除了8bit的资料,尚须包含2bit回应序列(Acknowledge Sequence),作为侦测错误之用,如图10。

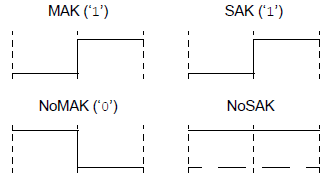

回应序列(Acknowledge Sequence)

UNI/O的回应序列中,第一个为主机回应(Master Acknowledge, MAK),由主机所产生;另一

个为从机回应(Slave Acknowledge, SAK),由从机产生。而主机回应和从机回应都需藉由回应

值来判断是属于哪种回应方式,主机回应值为1(MAK);表示主机传达该总线运作无误且

将持续进行的讯息传给从机,主机回应值为0(NoMAK);表示前一个byte为最后一笔传送的

资料,总线将停止运作。从机回应值为1(SAK);表示前一笔资料已正确地传给从机,且

从机接收到主机回应(MAK);从机回应值不为1(SAK)就为NoSAK,图11为回应序列种类图。

图11

图11Standby Pulse

Standby Pulse是由主机所产生,主要是重置(Reset)从机之用。该脉波宽度至少维持在高电位

600us左右。

Start Header

图12

图12Device Addressing

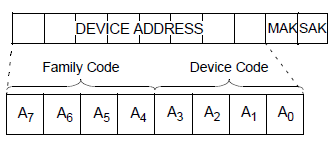

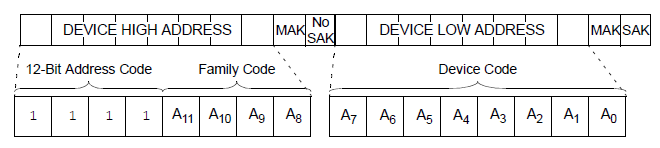

8-bit Device Addressing

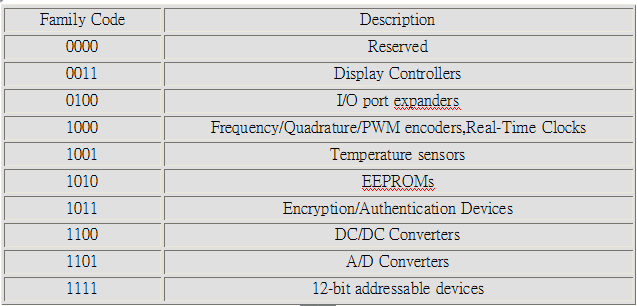

8 bit的定址方式,表示可以一个byte的来传达总线上所有的装置位址。前4个bit为Family

Code,后4个bit为Device Code。Family和Device Code这种组合即代表在总线上可以

有多个同种类的装置,即是使用相同的Family Code;不同的Device Code,图13为Family

Code所代表的装置,图14为示意图。

图13

图14

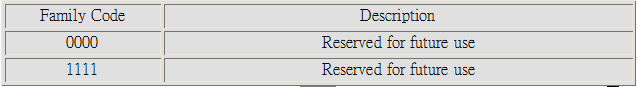

图1412-bit Device Addressing

12bit的定址方式是针对8bit定址方式扩充装置位址,完全兼容于8bit定址方式,参考图

15和图16。

图15

图16

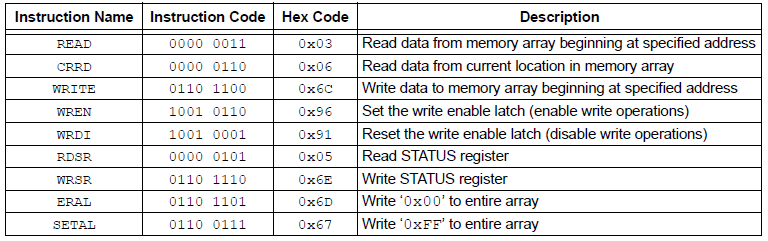

图16Command Structure

主机决定好从机之后,主机将会传送一个特殊命令给从机。这些命令可以由从机装置

的设计者来定义,本例是以EEPROM作为说明,图17为EEPROM的指令集。

图17

图17